# Highly Integrated Media Access Controller Programmer's Guide

## **REVISION HISTORY**

| Revision            | Date     | Change Description |

|---------------------|----------|--------------------|

| 57710_57711-PG200-R | 09/25/09 | Initial release.   |

Broadcom Corporation 5300 Calilfornia Avenue Irvine, CA 92617

© 2009 by Broadcom Corporation All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, the Connecting everything logo, NetXTreme II<sup>®</sup>, and RemotePHY<sup>™</sup> are among the trademarks of Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks or trade names mentioned are the property of their respective owners.

## TABLE OF CONTENTS

| Section 1: Introduction                                           | 1    |

|-------------------------------------------------------------------|------|

| Functional Description                                            | 1    |

| Supported Devices                                                 | 2    |

| Abbreviations and Definitions                                     | 2    |

| Section 2: Hardware Architecture                                  | 5    |

| Theory of Operations                                              | 5    |

| TCP-Offload                                                       | 7    |

| iSCSI Offload                                                     | 8    |

| Remote PHY                                                        | . 11 |

| Basic Operation Between Device and Remote Copper PHY              | . 11 |

| SerDes                                                            | . 13 |

| MAC                                                               | . 15 |

| Receive Front End                                                 | . 16 |

| Network Interface Glue                                            | . 16 |

| Arbiter/Filter                                                    | . 16 |

| Big Receive Buffer                                                | . 16 |

| Parser                                                            | . 16 |

| Searcher                                                          | . 17 |

| TSTORM (aka L4 Rx Processor or TCP Rx Processor)                  | . 17 |

| USTORM (aka L5 Rx Processor or ULP Rx Processor)                  | . 17 |

| XSTORM (aka Tx Processor)                                         | . 18 |

| CSTORM (aka Ack/Completion Processor)                             | . 18 |

| Segmentation and Framing Unit (aka Packet Builder and Framer-PBF) | . 18 |

| Marker and CRC Removal (aka ULP Packet Builder-UPB)               | . 18 |

| PCIe                                                              | . 19 |

| Management Control Processor                                      | . 19 |

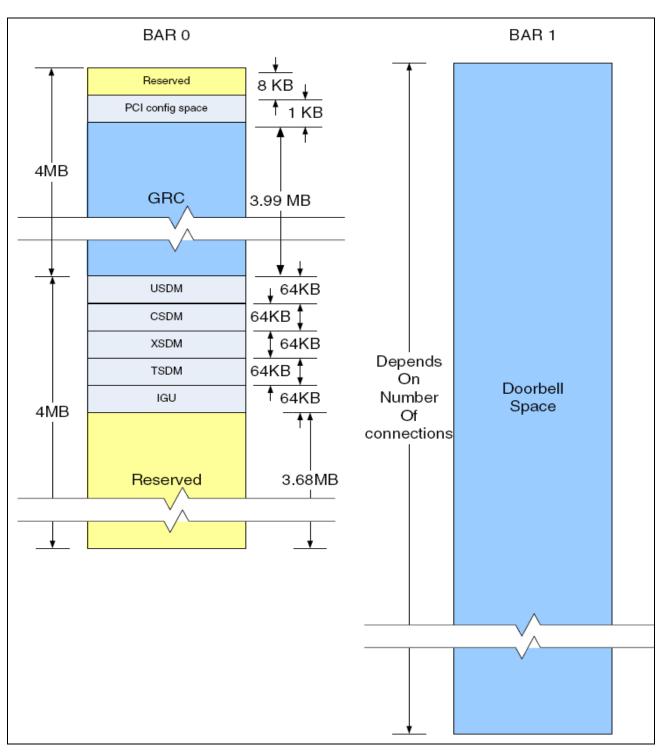

| Device Address Space                                              | . 19 |

| Host Bar Memory Map                                               | . 19 |

| MCP Memory Map                                                    | . 23 |

| Section 3: NVRAM Configuration                                    | .24  |

| NVRAM Map                                                         | . 24 |

| Code Directory                                            | 26 |

|-----------------------------------------------------------|----|

| Manufacturing Information                                 | 27 |

| Feature Configuration Information                         | 35 |

| Virtual Product Data Region                               | 43 |

| Program Images                                            | 43 |

| Calculating the CRC 32 Checksum                           | 44 |

| Flash Controller                                          | 45 |

| Self Configuration                                        | 46 |

| Atmel Page Sizes                                          | 47 |

| Programming the Non-Volatile Memory                       | 49 |

| Section 4: Data Structures                                | 50 |

| Host Memory L2 Data Structures                            | 50 |

| Virtual Versus Physical Address Views                     | 50 |

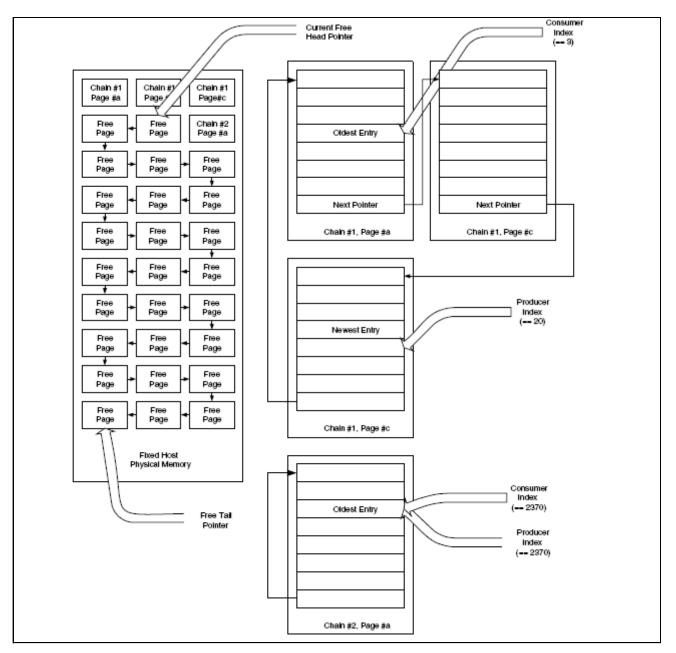

| Buffer Descriptor Chains                                  | 52 |

| RX Buffer Descriptor Format                               | 53 |

| RX Completion Queue Entry Format                          | 54 |

| Fast Path Rx CQE                                          | 54 |

| Ramrod Rx CQE                                             | 55 |

| Next Page Rx CQE                                          | 55 |

| TX Buffer Descriptor Format                               | 56 |

| Tx Parsing Information BD                                 | 57 |

| Next Page Tx BD                                           | 58 |

| Status Block Format                                       | 58 |

| Fast Path Status Block                                    | 58 |

| Default Status Block                                      | 58 |

| Section 5: Host Driver Flows                              | 59 |

| Device Initialization and Shutdown                        | 59 |

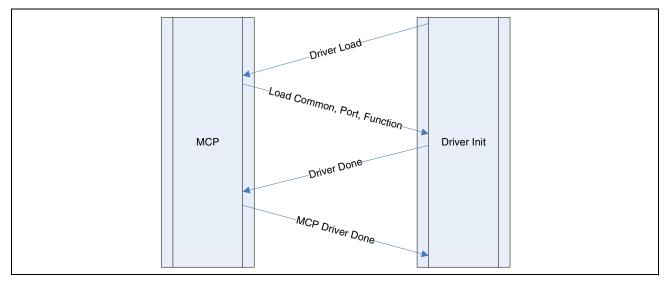

| MCP Interface                                             | 60 |

| Heart Beat/Pulse                                          | 61 |

| NIG Drain                                                 | 62 |

| Hardware Block Initialization and STORM Firmware Download | 62 |

| Host Driver Initialization                                | 62 |

| Ramrod                                                    | 63 |

| Device Shutdown                                           | 65 |

|     | errupt Handling and Attention                                                                                                                                                   | . 65                                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|     | Interrupt modes                                                                                                                                                                 | . 65                                                 |

|     | BCM57710/BCM57711 Interrupt generation                                                                                                                                          | . 65                                                 |

|     | Status Blocks                                                                                                                                                                   | . 66                                                 |

|     | ISR Mode                                                                                                                                                                        | . 68                                                 |

|     | Interrupt Configuration and Control                                                                                                                                             | . 68                                                 |

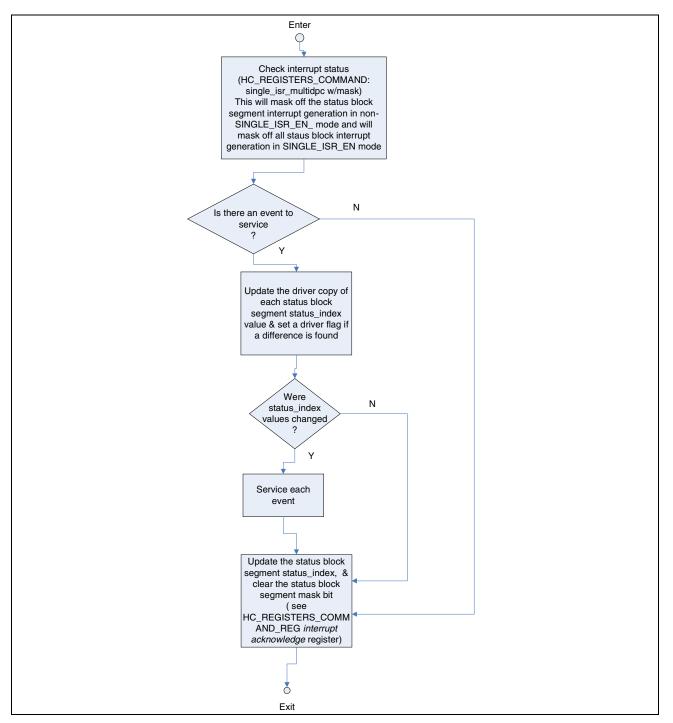

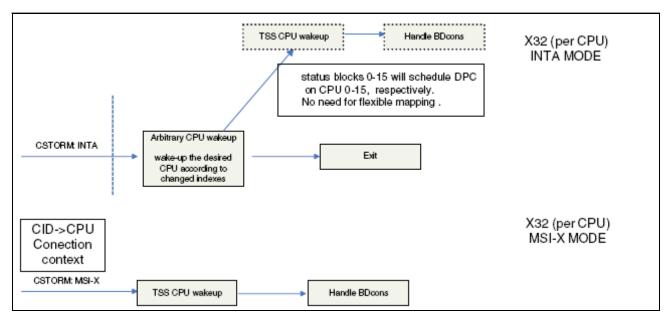

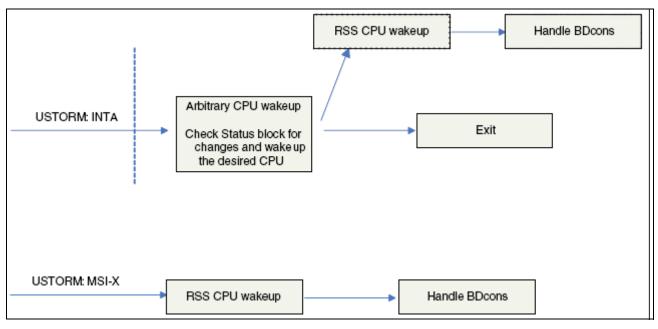

|     | Host Driver Interrupt Handler Flow                                                                                                                                              | . 69                                                 |

|     | HC Registers                                                                                                                                                                    | . 71                                                 |

|     | Attention Signals                                                                                                                                                               | . 79                                                 |

|     | Attention Routing                                                                                                                                                               | . 80                                                 |

|     | Signal Monitoring                                                                                                                                                               | . 80                                                 |

|     | Masking                                                                                                                                                                         | . 80                                                 |

|     | Dynamic vs. Static Interrupt Groups                                                                                                                                             | . 81                                                 |

|     | Attention Initialization by the Host Driver                                                                                                                                     | . 81                                                 |

|     | Handling Attentions in the Host Driver                                                                                                                                          | . 82                                                 |

| L2  | Transmit Flow                                                                                                                                                                   | . 85                                                 |

|     | ASIC/Firmware Flow                                                                                                                                                              | . 85                                                 |

|     | Driver Flow                                                                                                                                                                     | . 86                                                 |

|     | Tx Interrupt Handling                                                                                                                                                           | . 88                                                 |

| L2  | Receive Flow                                                                                                                                                                    | . 89                                                 |

|     | ASIC Flow                                                                                                                                                                       | . 89                                                 |

|     | TStorm                                                                                                                                                                          | . 90                                                 |

|     | USTORM                                                                                                                                                                          | . 90                                                 |

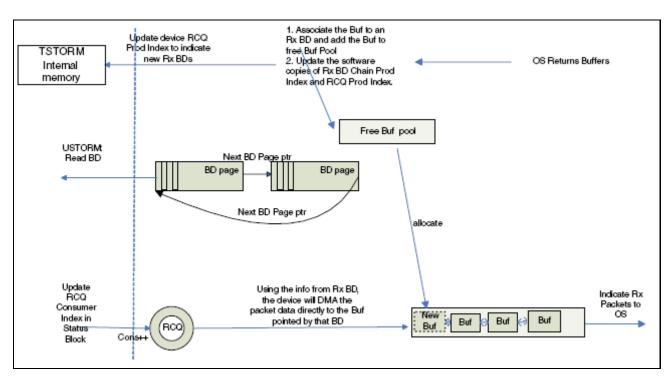

|     | Driver Flow                                                                                                                                                                     | . 91                                                 |

|     | Rx Interrupt Handling                                                                                                                                                           | . 93                                                 |

|     |                                                                                                                                                                                 |                                                      |

|     | Interrupt Coalescing                                                                                                                                                            | . 94                                                 |

| Tra | Interrupt Coalescing                                                                                                                                                            |                                                      |

| Tra |                                                                                                                                                                                 | . 95                                                 |

| Tra | nsparent Packet Aggregation                                                                                                                                                     | . 95<br>. 95                                         |

| Tra | Glossary                                                                                                                                                                        | . 95<br>. 95<br>. 95                                 |

| Tra | Glossary<br>Theory of Operations                                                                                                                                                | . 95<br>. 95<br>. 95<br>. 95                         |

| Tra | Insparent Packet Aggregation<br>Glossary<br>Theory of Operations<br>How Does Aggregation Work?                                                                                  | . 95<br>. 95<br>. 95<br>. 95<br>. 95                 |

| Tra | Insparent Packet Aggregation<br>Glossary<br>Theory of Operations<br>How Does Aggregation Work?<br>When to Aggregate?                                                            | . 95<br>. 95<br>. 95<br>. 95<br>. 96<br>. 97         |

| Tra | Insparent Packet Aggregation<br>Glossary<br>Theory of Operations<br>How Does Aggregation Work?<br>When to Aggregate?<br>When to Stop Aggregation?                               | . 95<br>. 95<br>. 95<br>. 95<br>. 96<br>. 97<br>. 97 |

| Tra | Insparent Packet Aggregation<br>Glossary<br>Theory of Operations<br>How Does Aggregation Work?<br>When to Aggregate?<br>When to Stop Aggregation?<br>Implementation Assumptions | . 95<br>. 95<br>. 95<br>. 95<br>. 96<br>. 97<br>. 97 |

| Firmware Data Structures               | 97  |

|----------------------------------------|-----|

| USTORM                                 | 97  |

| Host Data Structures                   |     |

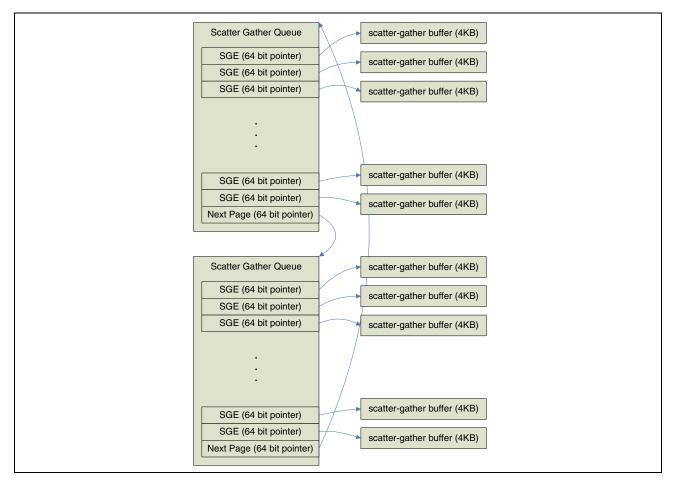

| Scatter Gather Queue                   |     |

| Scatter Gather Entry                   |     |

| Completion Queue Entry                 |     |

| High Level Outline                     |     |

| Initialization                         |     |

| Fastpath Operation                     |     |

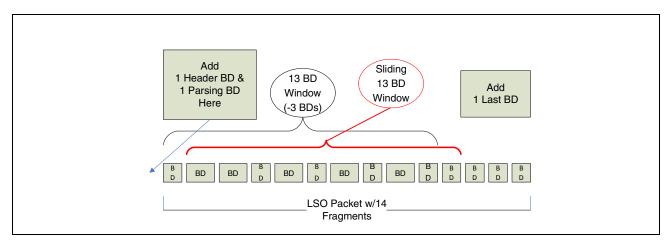

| Large Send Offload                     |     |

| Device Statistics                      | 104 |

| Direct Memory Access Engine (DMAE)     |     |

| The "Go" Register                      |     |

| The Opcode                             | 105 |

| Architecture                           |     |

| Section 6: PCIe                        | 108 |

| Introduction                           |     |

| Supported Features                     |     |

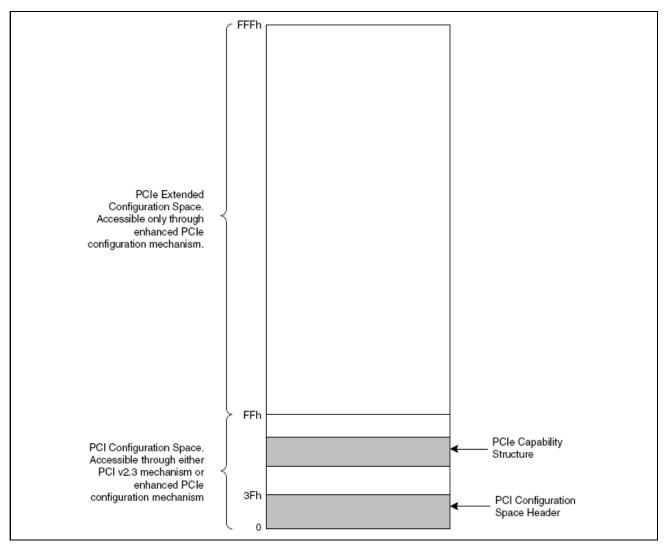

| Configuration Space                    | 111 |

| Required Registers                     | 112 |

| Capabilities Registers                 | 113 |

| Device-Specific Registers              | 113 |

| Expansion ROM                          | 113 |

| Operational Characteristics            | 113 |

| Section 7: Ethernet Link Configuration | 114 |

| Overview                               |     |

| MDIO Interface                         |     |

| Clause 22 Overview                     | 114 |

| Clause 45 Overview                     |     |

| Accessing PHY Registers                | 116 |

| Auto-Polling Mode                      | 116 |

| Bit-Bang Mode                          | 116 |

| Auto-Access Mode                       | 116 |

09/25/09

| Internal PHY                                    | 120 |

|-------------------------------------------------|-----|

| Appendix A: bxe_hsi.h                           |     |

| Appendix B: Programming the Non-Volatile Memory |     |

| NVRAM Access Example Code                       |     |

## LIST OF FIGURES

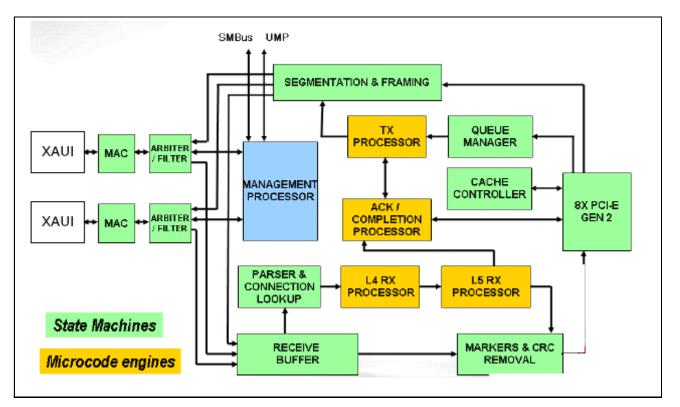

| Figure 1: | Functional Block Diagram                                      | 6   |

|-----------|---------------------------------------------------------------|-----|

| Figure 2: | Data Flow From Application Through Wire                       | 8   |

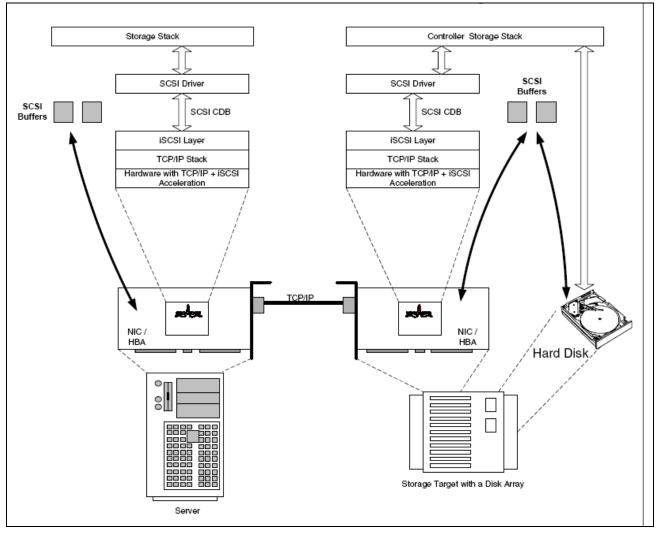

| Figure 3: | iSCSI Layers                                                  | 9   |

| Figure 4: | iSCSI Ethernet Frame Encapsulation                            | 9   |

| Figure 5: | iSCSI Architecture                                            | 10  |

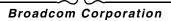

| Figure 6: | Simplified Hardware Architecture                              | 12  |

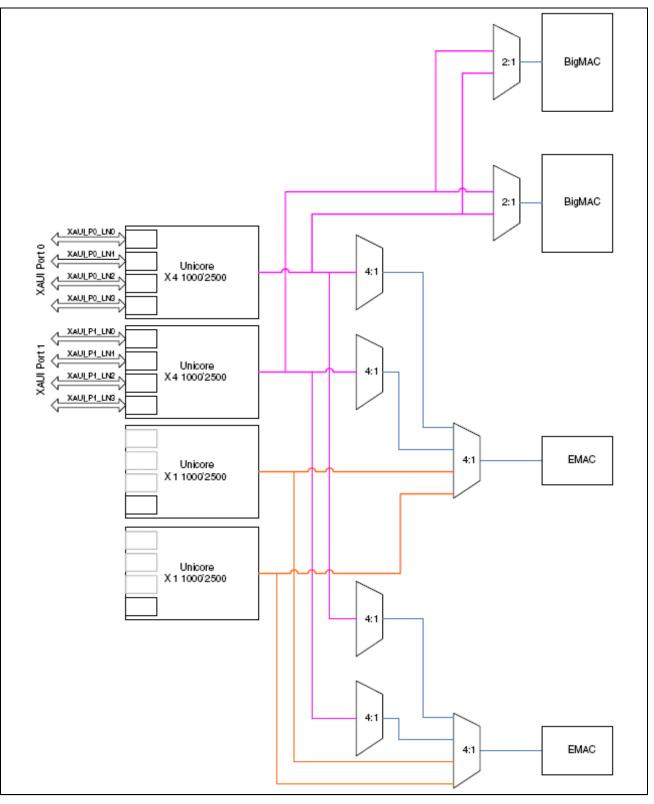

| Figure 7: | Multiplexing b/w XAUI and 1000BASE-KX/2500BASE-KX             | 14  |

| Figure 8: | BCM57710/BCM57711 BAR Memory Space                            | 22  |

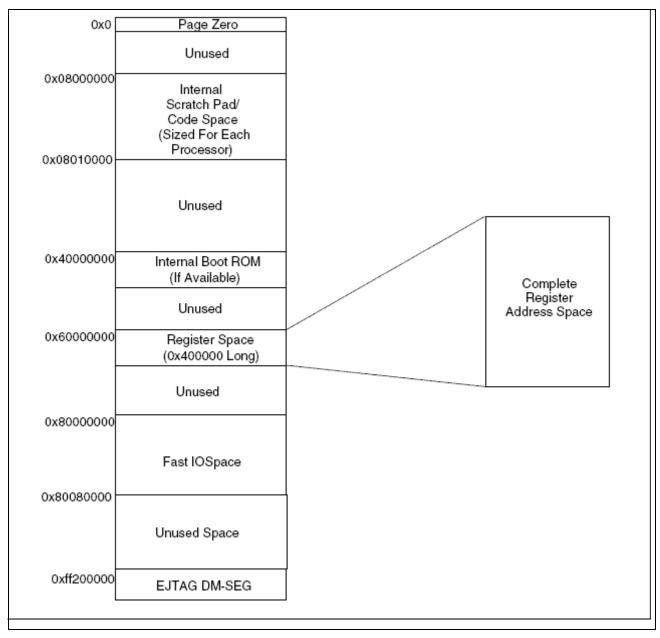

| Figure 9: | MCP Memory MAP                                                | 23  |

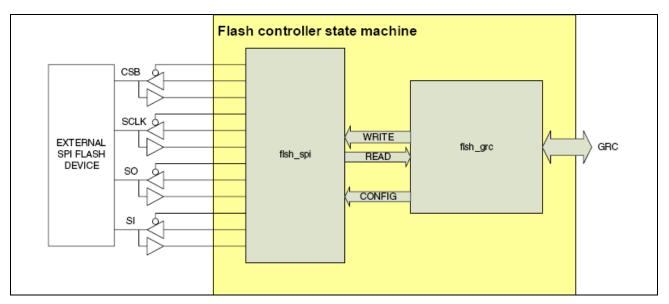

| Figure 10 | : Flash Controller State Machine and Interfaces               | 45  |

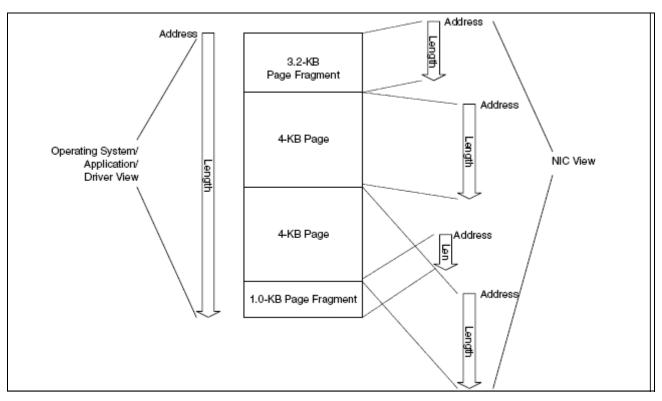

| Figure 11 | : Virtual Address versus Physical Address View                | 51  |

| Figure 12 | Chain With Multiple Pages                                     | 52  |

| Figure 13 | : Driver/MCP Handshake                                        | 61  |

| Figure 14 | : Handle Interrupt Flow                                       | 70  |

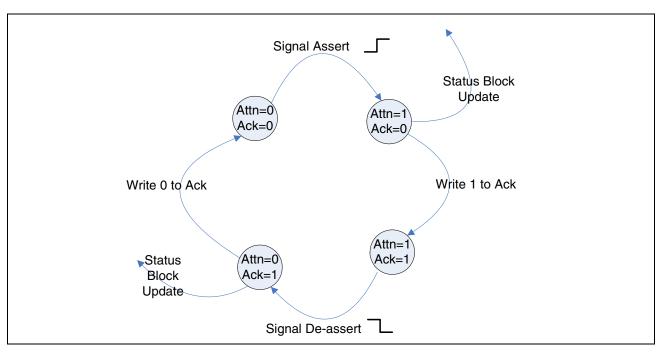

| Figure 15 | : Attention States                                            | 83  |

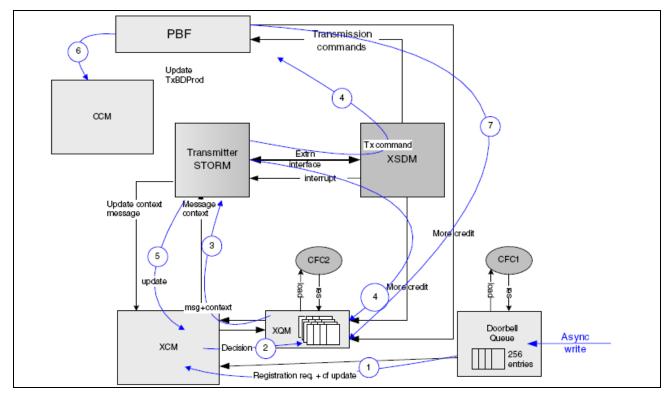

| Figure 16 | : L2 Tx Packet Flow Inside the ASIC                           | 85  |

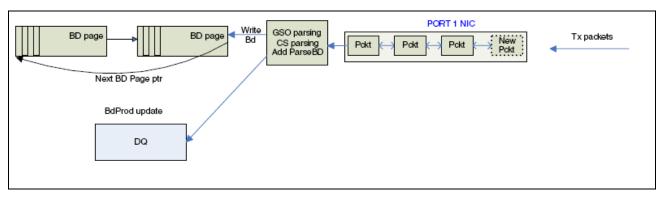

| Figure 17 | : L2 Tx Packet Flow                                           |     |

| Figure 18 | : Tx Packet Completion                                        |     |

| Figure 19 | Rx Driver Flow                                                | 92  |

| Figure 20 | Rx Interrupt Flow                                             | 93  |

| Figure 21 | : Scatter-Gather Queue Structure                              |     |

| Figure 22 | : 13 BD Sliding Window                                        |     |

| Figure 23 | PCIe Configuration Space                                      | 111 |

| Figure 24 | PCIe Type 0 Configuration Space Header                        | 112 |

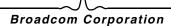

| Figure 25 | STA and MMD devices (ffrom the IEEE 802.3-2005 Specification) | 115 |

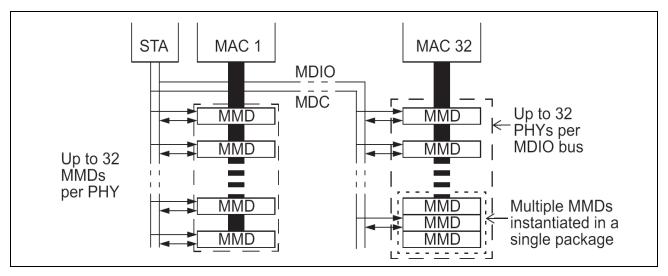

| Figure 26 | Address and Write Management Frames                           | 118 |

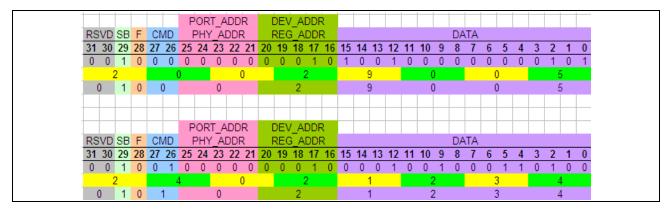

| Figure 27 | : Address and Read Management Frames                          | 119 |

# LIST OF TABLES

| Table 1:  | Supported Devices                                                                         | . 2 |

|-----------|-------------------------------------------------------------------------------------------|-----|

| Table 2:  | Abbreviations and Definitions                                                             | . 2 |

| Table 3:  | BCM57710/BCM57711 BAR0 Memory Map                                                         | 19  |

| Table 4:  | BCM57710/BCM57711 GRC Space Register Offsets                                              | 20  |

| Table 5:  | NVRAM Map                                                                                 | 24  |

| Table 6:  | Boot Strap Region                                                                         | 25  |

| Table 7:  | Code Directory Region                                                                     | 26  |

| Table 8:  | Manufacturing Information                                                                 | 27  |

| Table 9:  | Feature Configuration Region                                                              | 35  |

| Table 10: | Virtual Product Data Region                                                               | 43  |

| Table 11: | Program Images Region                                                                     | 43  |

| Table 12: | NVRAM Strapping Table                                                                     | 46  |

| Table 13: | Default (Slow Path) Status Block                                                          | 66  |

| Table 14: | TX/RX (Fast Path) Status Block                                                            | 68  |

| Table 15: | HC_REGISTERS_CONFIG_0 (Offset: 0x108000; Width: 32)                                       | 71  |

| Table 16: | HC_REGISTERS_COMMAND_REG (Offset: 0x108180) - Interrupt Acknowledge Port 0                | 71  |

| Table 17: | HC_REGISTERS_COMMAND_REG (Offset: 0x108184) - Producer Update Port 0                      | 72  |

| Table 18: | HC_REGISTERS_COMMAND_REG (Offset: 0x108188) - Attention Bit Update Port 0                 | 73  |

| Table 19: | HC_REGISTERS_COMMAND_REG (Offset: 0x10818C) - Attention Bit Set Port 0                    | 74  |

| Table 20: | HC_REGISTERS_COMMAND_REG (Offset: 0x108190) - Attention Bit Clear Port 0                  | 74  |

| Table 21: | HC_REGISTERS_COMMAND_REG (Offset: 0x108194) - Coalesce Now Port 0                         | 74  |

| Table 22: | HC_REGISTERS_COMMAND_REG (Offset: 0x108198) -<br>Single_isr_multi_dpc With Mask Port 0    | 74  |

| Table 23: | HC_REGISTERS_COMMAND_REG (Offset: 0x10819C) -<br>Single_isr_multi_dpc Without Mask Port 0 | 75  |

| Table 24: | HC_REGISTERS_COMMAND_REG (Offset: 0x108200) - Interrupt Acknowledge Port 1                | 75  |

| Table 25: | HC_REGISTERS_COMMAND_REG (Offset: 0x108204) - Producer Update Port 1                      | 76  |

| Table 26: | HC_REGISTERS_COMMAND_REG (Offset: 0x108208) - Attention Bit Update Port 1                 | 77  |

| Table 27: | HC_REGISTERS_COMMAND_REG (Offset: 0x10820C) - Attention Bit Set Port 1                    | 78  |

| Table 28: | HC_REGISTERS_COMMAND_REG (Offset: 0x108210) - Attention Bit Clear Port 1                  | 78  |

| Table 29: | HC_REGISTERS_COMMAND_REG (Offset: 0x108214) - Coalesce Now Port 1                         | 78  |

| Table 30: | HC_REGISTERS_COMMAND_REG (Offset: 0x108218) -<br>Single_isr_multi_dpc With Mask Port 1    | 78  |

| Table 31: | HC_REGISTERS_COMMAND_REG (Offset: 0x10821C) -                                             |     |

|           | Single_isr_multi_dpc Without Mask Port 1                                                       | 79  |

|-----------|------------------------------------------------------------------------------------------------|-----|

| Table 32: | Static Attention Routing for Function 0                                                        | 81  |

| Table 33: | Static Attention Routing for Function 1                                                        | 81  |

| Table 34: | VLAN Filtering Rules                                                                           | 90  |

| Table 35: | Opcode Format                                                                                  | 105 |

| Table 36: | PCIe Features                                                                                  | 109 |

| Table 37: | Management Frame Format (See IEEE 802.3-2005 Specification)                                    | 114 |

| Table 38: | Clause 45 MDIO Management Frame Formats                                                        | 115 |

| Table 39: | EMAC_REG_EMAC_MDIO_MODE - (Offset: (GRCBASE_EMAC0 / GRCBASE_EMAC1)<br>+ 0xB4; Width: 32)       | 117 |

| Table 40: | Internal PHY Clause 45 Register Blocks                                                         | 120 |

| Table 41: | IEEE0 Clause 73 Autonegotiation Control Register<br>(Offset: 0x0; Width: 16) AKA (CL73_IEEEB0) | 121 |

| Table 42: | IEEE0 Clause 73 Autonegotiation Status Register (Offset: 0x1 Width: 16)                        | 121 |

| Table 43: | IEEE0 Clause 73 Autonegotiation PHY ID MSB Register (Offset: 0x2 Width: 16)                    | 122 |

| Table 44: | IEEE0 Clause 73 Autonegotiation PHY ID LSB Register (Offset: 0x3 Width: 16)                    | 122 |

| Table 45: | IEEE0 CL73 Autonegotiation Devices in Package 1 Register (Offset: 0x5; Width: 16)              | 122 |

| Table 46: | IEEE0 CL 73 Autonegotiation Devices in Package 2 (Offset: 0x6; Width: 16)                      | 123 |

| Table 47: | CL73_IEEE1_CL73_AUTONEG_ADVERTISE (Offset: 0x1; Width: 16)                                     | 123 |

| Table 48: | TXALL Status 0 Register (Offset: 0x0000; Width: 16)                                            | 124 |

| Table 49: | TXALL Control 0 Register (Offset: 0x0007; Width: 16)                                           | 124 |

| Table 50: | TXALL MDIO Data 0 Register (Offset: 0x0012; Width: 16)                                         | 125 |

| Table 51: | TXALL MDIO Data 1 Register (Offset: 0x0013; Width: 16)                                         | 125 |

| Table 52: | TXALL Status 1 Register (Offset: 0x0014; Width: 16)                                            | 125 |

| Table 53: | TXALL BG VCM Register (Offset: 0x0015; Width: 16)                                              | 125 |

| Table 54: | TXALL IBuff 1T2T Register (Offset: 0x0016; Width: 16)                                          | 126 |

| Table 55: | TXALL Transmit Driver Register (Offset: 0x0017; Width 16)                                      | 127 |

| Table 56: | RXALL Receive Status Register (Offset: 0x0; Width: 16)                                         | 129 |

| Table 57: | RXALL Receive Control Register (Offset: 0x01; Width 16)                                        | 129 |

| Table 58: | RXALL Receive Timer 1 Register (Offset: 0x02; Width 16)                                        | 130 |

| Table 59: | RXALL Receive Timer 2 Register (Offset: 0x03; Width 16)                                        | 130 |

| Table 60: | RXALL Receive Signal Detect Register (Offset: 0x04; Width 16)                                  | 130 |

| Table 61: | RXALL Receive CDR Phase Register (Offset: 0x05; Width 16)                                      | 130 |

| Table 62: | RXALL Receive CDR Frequency Register (Offset: 0x06; Width 16)                                  | 131 |

| Table 63: | RXALL Receive Equalizer Configuration Register (Offset: 0x07; Width)                           | 131 |

09/25/09

| Table 64: RXALL Receive Equalizer Force Register (Offset: 0x08; Width 16)                | 131 |

|------------------------------------------------------------------------------------------|-----|

| Table 65: RXALL Receive Control 1G Register (Offset: 0x09; Width 16)                     |     |

| Table 66: RXALL Receive Control PCI Express Register (Offset: 0x0A; Width 16)            |     |

| Table 67: RXALL Receive All Status Register (Offset: 0x0B; Width 16)                     |     |

| Table 68: RXALL Receive Equalizer Boost Register (Offset: 0x0C; Width 16)                |     |

| Table 69: RXALL Receive Ib Data Equalizer Register (Offset: 0x0D; Width 16)              |     |

| Table 70: RXALL Receive Ib ADC Buffer Register (Offset: 0x0E; Width 16)                  |     |

| Table 71: XGXS BLOCK 2 RX LANE SWAP (Offset: 0x0; Width 16)                              |     |

| Table 72: XGXS BLOCK 2 TX LANE SWAP (Offset: 0x1; Width 16)                              |     |

| Table 73: XGXS BLOCK 2 UNI-core Mode (Offset: 0x04; Width 16)                            |     |

| Table 74: XGXS BLOCK Test Mode Lane (Offset: 0x05; Width 16)                             | 135 |

| Table 75: GP Status Miscellaneous RX Status Register (Offset: 0x0; Width 16)             | 135 |

| Table 76: GP Status XGXS Status 0 Register (Offset 0x01; Width 16)                       |     |

| Table 77: GP Status XGXS Status 1 Register (Offset 0x02; Width 16)                       |     |

| Table 78: GP Status XGXS Status 2 Register (Offset 0x03; Width 16)                       | 137 |

| Table 79: GP Status 1000X Status 1 Register (Offset: 0x04; Width 16)                     | 137 |

| Table 80: GP Status 1000X Status 2 Register (Offset: 0x05; Width 16)                     | 138 |

| Table 81: GP Status 1000X Status 3 Register (Offset: 0x06; Width 16)                     | 140 |

| Table 82: GP Status TPOUT 1 Register (Offset: 0x07; Width 16)                            | 140 |

| Table 83: GP Status TPOUT 2 Register (Offset: 0x08; Width 16)                            | 140 |

| Table 84: GP Status XGXS Status 3 Register (Offset: 0x09; Width 16)                      | 140 |

| Table 85: GP Status x2500 Status 1 Register (Offset: 0x0A; Width 16)                     | 141 |

| Table 86: GP Status Top Autonegotiation Status Register (Offset: 0x0B; Width 16)         | 141 |

| Table 87: GP Status LP_UP1 Register (Offset: 0x0C; Width 16)                             | 142 |

| Table 88: GP Status LP_UP2 Register (Offset: 0x0D; Width 16)                             | 142 |

| Table 89: GP Status LP_UP3 Register (Offset: 0x0E; Width 16)                             | 143 |

| Table 90: SerDes Digital 1000X Control 1 Register (Offset: 0x0; Width 16)                | 143 |

| Table 91: SerDes Digital 1000X Control 2 Register (Offset: 0x01; Width 16)               | 144 |

| Table 92: SerDes Digital 1000X Control 3 Register (Offset: 0x02; Width 16)               | 145 |

| Table 93: SerDes Digital 1000X Control 4 Register (Offset: 0x03; Width 16)               | 146 |

| Table 94: SerDes Digital 1000X Status 1 Register (Offset: 0x04; Width 16)                | 147 |

| Table 95:       SerDes Digital 1000X       Status 2 Register (Offset: 0x05; Width 16)    | 148 |

| Table 96: SerDes Digital 1000X Status 3 Register (Offset: 0x06; Width 16)                | 148 |

| Table 97: SerDes Digital CRC Err and Rx Packet Counter Register (Offset: 0x07; Width 16) | 148 |

| Table 98: SerDes Digital Miscellaneous 1 Register (Offset: 0x08; Width 16)               | 149 |

|                                                                                          |     |

|                                                                                                  | _  |

|--------------------------------------------------------------------------------------------------|----|

| Table 99: SerDes Digital Miscellaneous 2 Register (Offset: 0x09; Width 16)       14              | .9 |

| Table 100:SerDes Digital Pattern Generation Control Register (Offset: 0x0A; Width 16)         15 | 60 |

| Table 101:SerDes Digital Pattern Generation Status Register (Offset: 0x0B; Width 16)15           | 51 |

| Table 102:SerDes Digital Test Mode Register (Offset: 0x0C; Width 16)       15                    | 51 |

| Table 103:SerDes Digital Transmit Packet Count Register (Offset: 0x0D; Width 16)15               | 62 |

| Table 104:SerDes Digital Receive Packet Count Register (Offset: 0x0E; Width 16)15                | 62 |

| Table 105:Over 1G Digital Control 30 Register (Offset: 0x0; Width 16)15                          | 62 |

| Table 106:Over 1G Digital Control 31 Register (Offset: 0x1; Width 16)                            | 62 |

| Table 107:Over 1G Digital Control 32 Register (Offset: 0x2; Width 16)15                          | 52 |

| Table 108:Over 1G Digital Control 33 Register (Offset: 0x3; Width 16)15                          | 52 |

| Table 109:Over 1G Digital Control 34 Register (Offset: 0x04; Width 16)15                         | 3  |

| Table 110:Over 1G Digital Control 35 Register (Offset: 0x05; Width 16)15                         | 3  |

| Table 111:Over 1G Digital Control 36 Register (Offset: 0x06; Width 16)15                         | 3  |

| Table 112:Over 1G TPOUT 1 Register (Offset: 0x07; Width 16)15                                    | 3  |

| Table 113:Over 1G TPOUT 2 Register (Offset: 0x08; Width 16)15                                    | 64 |

| Table 114:Over 1G Unformatted Page 1 Register (Offset: 0x09; Width 16)15                         | 64 |

| Table 115:Over 1G Unformatted Page 2 Register (Offset: 0x0A; Width 16)15                         | 64 |

| Table 116:Over 1G Unformatted Page 3 Register (Offset: 0x0B; Width 16)15                         | 64 |

| Table 117:Over 1G Link Partner Unformatted Page 1 Register (Offset: 0x0C; Width 16)15            | 64 |

| Table 118:Over 1G LP_UP 2 Register Offset: 0x0D; Width 16)15                                     | 5  |

| Table 119:Over 1G LP_UP 3 Register (Offset: 0x0E; Width 16)15                                    | 5  |

| Table 120:MRBE Message Page 5 Next Page Control Register (Offset: 0x0; Width 16)15               | 5  |

| Table 121:MRBE Link Timer Offset 1 Register (Offset: 0x01; Width 16)15                           | 5  |

| Table 122:MRBE Link Timer Offset 2 Register (Offset: 0x02; Width 16)                             | 6  |

| Table 123:MRBE Link Timer Offset 3 Register (Offset: 0x03; Width 16)                             | 6  |

| Table 124:MRBE OUI MSB Field Register (Offset: 0x04; Width 16)15                                 | 6  |

| Table 125:MRBE OUI LSB Field Register (Offset: 0x05; Width 16)15                                 | 6  |

| Table 126:MRBE Field Register (Offset: 0x06; Width 16)                                           | 6  |

| Table 127:MRBE UD Field Register (Offset: 0x07; Width 16)       15                               | 57 |

| Table 128:MRBE Link Partner OUI MSB Field Register (Offset: 0x08; Width 16)15                    | 57 |

| Table 129:MRBE Link Partner OUI LSB Field Register (Offset: 0x09; Width 16)15                    | 57 |

| Table 130:MRBE Link Partner MRBE Field Register (Offset: 0x0A; Width 16)15                       | 57 |

| Table 131:MRBE Link Partner UD Field Register (Offset: 0x0B; Width 16)15                         | 57 |

| Table 132:CL73_UserB0 Control 1 Register (Offset: 0x00; Width 16)15                              | 8  |

| Table 133:CL73_UserB0 Status 1 Register (Offset: 0x01; Width 16)15                               | 8  |

| Table 134:CL73_UserB0 MRBE Control 1 Register (Offset: 0x02; Width 16)                   | 159 |

|------------------------------------------------------------------------------------------|-----|

| Table 135:CL73_UserB0 MRBE Control 2 Register (Offset: 0x03; Width 16)                   | 159 |

| Table 136:CL73_UserB0 MRBE Control 3 Register (Offset: 0x04; Width 16)                   | 159 |

| Table 137:CL73_UserB0 MRBE Status 1 Register (Offset: 0x05; Width 16)                    | 159 |

| Table 138:CL73_UserB0 MRBE Status 2 Register (Offset: 0x06; Width 16)                    | 160 |

| Table 139:CL73_UserB0 MRBE Status 3 Register (Offset: 0x07; Width 16)                    | 160 |

| Table 140:AER Address Extension Register (Offset: 0x0E; Width 16)                        | 160 |

| Table 141:IEEE_Combo MII Control Register (Offset: 0x0; Width 16)                        | 161 |

| Table 142:IEEE0 MII Status Register (Offset: 0x01; Width 16)                             | 161 |

| Table 143:IEEE0 PHY Identifier MSB Register (Offset: 0x02; Width 16)                     | 162 |

| Table 144:IEEE0 PHY Identifier LSB Register (Offset: 0x03; Width 16)                     | 162 |

| Table 145:IEEE0 Autonegotiation Advertisement Register (Offset: 0x04; Width 16)          | 163 |

| Table 146:IEEE0 Autonegotiation Link Partner Ability Register (Offset: 0x05; Width 16)   | 163 |

| Table 147:IEEE0 Autonegotiation Expansion Register (Offset: 0x06; Width 16)              | 163 |

| Table 148:IEEE0 Autonegotiation Next Page Register (Offset: 0x07; Width 16)              | 164 |

| Table 149:IEEE0 Autonegotiation Link Partner Next Page Register (Offset: 0x08; Width 16) | 164 |

# Section 1: Introduction

Throughout this document, the term Broadcom<sup>®</sup> NetXtreme II<sup>®</sup> refers to the Broadcom BCM57710/BCM57711 Dual Port 10-Gigabit Ethernet Controllers. The BCM577XX 10-Gigabit Ethernet controllers refer to the Broadcom BCM57710 and the BCM57711 controllers. The reader is urged to view the Broadcom Open Source FreeBSD or Linux<sup>®</sup> driver as a code reference and companion to this document. The Firmware component of the BCM57710/BCM57711 is vital to the BCM57710/BCM57711 host driver and device functionality. Developers writing custom drivers must be aware of the required hardware and software interface data structures used in specific versions of driver firmware. Changes in the software and firmware are evident in the Open Source drivers. This document primarily covers the device layer two and layer three functionality in host driver software along with an overview of the BCM57710/BCM57711 hardware architecture.

This document includes data structures specific to the device firmware version 4.8.5. See Appendix B "Programming the Non-Volatile Memory" for an example of data structures common to the host driver and device firmware.

## **FUNCTIONAL DESCRIPTION**

Broadcom NetXtreme II includes dedicated hardware and internal microprocessors to process frames. Four on-chip highperformance VLIW STate Optimized RISC Microprocessors (also known as STORMs) enable layer four (L4) and layer five (L5) offload features, including TCP segmentation, full TCP Offload processing, iSCSI offload, and RDMA offload. On the transmit path, the Broadcom NetXtreme II extracts data directly from application buffer space on the host, executes any relevant L5 protocol such as the TCP/IP protocol, adds the required TCP/IP, iSCSI 1.0, or RDMA headers and then transmits the data over the physical medium. On the receive path, the Broadcom NetXtreme II processes the frame up to the highest supported layer. It removes lower-level headers from the incoming frames received from the physical interface and optionally places the data directly to application buffer space, again sparing host CPU resources that would otherwise be required for copying data between user buffers and kernel buffers.

For iSCSI functionality, the Broadcom NetXtreme II provides a hardware offload for the most host-CPU-intensive tasks. For the transmit data path, the Broadcom NetXtreme II adds framing support and calculates the header and data digest. On the receive data path, the Broadcom NetXtreme II strips the framing headers and checks CRC, then stores the data in the designated iSCSI buffers. Broadcom NetXtreme II builds iSCSI command PDUs and processes iSCSI response PDUs, offloading the host CPU from this task. Broadcom NetXtreme II DMA data directly to/ from application buffers, sparing host CPU resources that would otherwise be required for copying data between user buffers and kernel buffers.

The Broadcom NetXtreme II also supports other major features like Receive Side Scaling (RSS) for short-lived TCP connections, guaranteed delivery of management packets, RemotePHY<sup>™</sup> functionality, and advanced congestion management. RSS allows for more balanced load sharing in an SMP server, handling a load of short-lived connections. The guaranteed delivery of management packets provides QoS for management traffic and allows management applications running on Remote Management Console (RMC) to talk to BMC even when there is congestion because of CPU inability to service faster than the incoming traffic. On the transmit side, management traffic coming from BMC takes strict priority over data coming from the host. The RemotePHY feature allows the local SerDes to interface to a Remote 10/100/1000BASE-T copper PHY via a backplane and to control and configure the RemotePHY in-band using the SerDes interface supporting the Broadcom Autonegotiation Mode (BAM) which utilizes the IEEE 802.3 next page capabilities in Clause 37. The advanced congestion management functionality like Service Aware Flow Control (SAFC) allows flow control and rate limiting per a given Class of Service.

The integrated 1-Gbps and 10-Gbps MACs are IEEE 802.3-compliant and support 802.1Q VLAN tagging, 802.1p layer 2 priority encoding, and 802.3x full-duplex flow control. The integrated transceivers are fully compatible with the IEEE 802.3

standard for autonegotiation of speed. Additionally, the device supports real-time tracing, loopbacks, and extensive statistics for debugging and diagnostic purposes.

## SUPPORTED DEVICES

Broadcom Devices with the following PCIE Device IDs are the focus of this document. The PCIE Device ID value is found in PCIE Configuration space at offset 0x2, or through the GRC address space at PCIE\_REG\_PCIER\_CFG\_DEVICE\_ID - (Offset: 0x2002; Width: 16).

| Table | 1: | Supported Devices |

|-------|----|-------------------|

| 10010 |    |                   |

| Device   | PCI Device ID |

|----------|---------------|

| BCM57710 | 0x164e        |

| BCM57711 | 0x164f        |

## **ABBREVIATIONS AND DEFINITIONS**

Table 2 shows abbreviations and definitions used in this document.

| Abbreviation | Definition                                        |

|--------------|---------------------------------------------------|

| ACPI         | Advanced Configuration and Power Interface        |

| BCN          | Backwards Congestion Notification                 |

| BMC          | Baseboard Management Controller                   |

| CAM          | Content Addressable Memory                        |

| CID          | Connection ID                                     |

| CMOS         | Complimentary Metal Oxide Semiconductor           |

| CNIC         | Converged NIC                                     |

| CRC          | Cyclic Redundancy Check                           |

| DDP          | Direct Data Placement                             |

| FIC          | Fast Input Channel                                |

| FOC          | Fast Output Channel                               |

| GMII         | Gigabit Media Independent Interface               |

| GRC          | Global Register Controller                        |

| GSO          | Giant Send Offload                                |

| JTAG         | Joint Test Action Group                           |

| HBA          | Host Bus Adapter                                  |

| IEEE         | Institute of Electrical and Electronics Engineers |

| iSCSI        | internet Small Computers System Interface         |

| iSER         | iSCSI Extensions for RDMA                         |

| IF           | Interface                                         |

| IPG          | Inter Packet Gap                                  |

| Abbreviation | Definition                                                                                                     |  |

|--------------|----------------------------------------------------------------------------------------------------------------|--|

| IPMI         | Intelligent Platform Management                                                                                |  |

| ILAN         | Interface Local Area Network                                                                                   |  |

| LCID         | Local Connection ID                                                                                            |  |

| LFSR         | Linear Feedback Shift Register                                                                                 |  |

| LOM          | LAN On Motherboard                                                                                             |  |

| LSO          | Large Send Offload                                                                                             |  |

| MAC          | Media Access Control                                                                                           |  |

| MCP          | Management Communication Processor                                                                             |  |

| MDIO         | Management Data Input Output                                                                                   |  |

| MIB          | Management Information Base                                                                                    |  |

| MII          | Media Independent Interface                                                                                    |  |

| MSI          | Message Signal Interrupt                                                                                       |  |

| MSIX-X       | MSI eXtended                                                                                                   |  |

| MSS          | Maximum Segment Size                                                                                           |  |

| NIC          | Network Interface Card                                                                                         |  |

| OSI          | Open Systems Interface                                                                                         |  |

| PBF          | Packet Builder and Framer                                                                                      |  |

| PCS          | Physical Coding Sublayer                                                                                       |  |

| PHY          | Physical Interface                                                                                             |  |

| PMA          | Physical Medium Attachment                                                                                     |  |

| QoS          | Quality of Service                                                                                             |  |

| PDU          | Protocol Data Unit                                                                                             |  |

| PCI          | Peripheral Connect Interface                                                                                   |  |

| PCI-X        | PCI-eXtended                                                                                                   |  |

| PCle         | PCI Express <sup>®</sup>                                                                                       |  |

| RFE          | Receive Front End                                                                                              |  |

| RDMA         | Remote Direct Memory Transfer                                                                                  |  |

| RDMAC        | RDMA Consortium                                                                                                |  |

| RDMAP        | RDMA Protocol                                                                                                  |  |

| RMC          | Remote Management Console                                                                                      |  |

| RNIC         | RDMA capable NIC                                                                                               |  |

| ROM          | Read Only Memory                                                                                               |  |

| RSS          | Receive Side Scaling                                                                                           |  |

| SAFC         | Service Aware Flow Control                                                                                     |  |

| SerDes       | Serializer and Deserializer                                                                                    |  |

| SNMP         | Simple Network Management Protocol                                                                             |  |

| Tuple        | An ordered set of values.                                                                                      |  |

| TCP Tuple    | A tuple consisting of the source IP address, destination IP address, source TCP port, and destination TCP port |  |

| TSO          | TCP Segmentation Offload                                                                                       |  |

| ULP          | Upper Layer Protocol                                                                                           |  |

| UMP          | Universal Management Port                                                                                      |  |

#### Table 2: Abbreviations and Definitions (Cont.)

Λ

| Abbreviation | Definition                                              |  |

|--------------|---------------------------------------------------------|--|

| VLAN         | Virtual LAN                                             |  |

| WoL          | Wake on LAN                                             |  |

| XAUI         | 10 Gigabit Attachment Unit Interface                    |  |

| XFI          | 10 Gigabit small Form factor pluggable module Interface |  |

| XFP          | 10 Gigabit small Form factor Pluggable module           |  |

| XGMII        | 10 Gigabit Media Independent Interface                  |  |

| XPAK         | 10 Gigabit Ethernet Pluggable module                    |  |

|              |                                                         |  |

#### Table 2: Abbreviations and Definitions (Cont.)

# Section 2: Hardware Architecture

## THEORY OF OPERATIONS

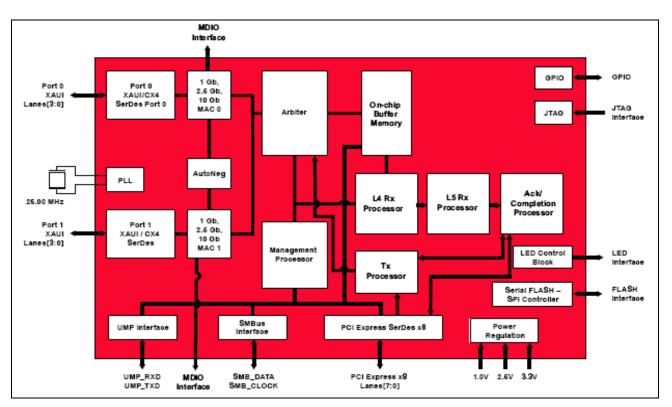

Figure 1 on page 6 shows the major functional blocks and interfaces of Broadcom NetXtreme II BCM57710/BCM57711 dual port 10 Gbps Ethernet controller. Each port includes an integrated SerDes device supporting 1000/2500 BASE-X, 10GBASE-CX4, 10GBASEKX4, and XAUI network interfaces and IEEE 802.3-compliant 1/2.5/10 Gbps MACs. Both ports share common blocks that are tuned for independent packet flows. The device's DMA engine provides DMA transactions from host memory to the device local storage, and vice-versa. The Broadcom NetXtreme II provides a PCIe v2.0 and v1.1-compliant bus interface. The RX MAC moves packets from the PHY into the device internal memory. All incoming packets are checked against a set of rules and then categorized accordingly.

When a packet is transmitted, the TX MAC moves the data from internal memory to the PHY. Both flows operate independently of each other in full-duplex mode. The device implements 128 KB of internal on-chip receive buffer memory and 25 KB per port of internal on-chip transmit buffer memory for temporarily storing the data before it is moved in and out of Ethernet and PCIe interfaces. The internal receive buffer memory is also commonly referred to as big RAM or the Big Receive Buffer (BRB). The device arbiter controls the access to the on-chip buffer memory.

Four high-performance VLIW RISC processors are implemented at strategic places in the device architecture such that they can be used in conjunction with other hardware blocks for L2 processing and supporting L4 and L5 offload features, including TCP segmentation, full TCP Offload, and iSCSI offload. One other RISC processor, referred as the Management Control Processor (MCP), is implemented to execute the boot-code and the firmware supporting driver initialization and shutdown synchronization and advanced management functions like IPMI Pass-Through or UMP or NC-SI. All five RISC processors and the on-chip buffer memory are shared between the two Ethernet ports. For management the UMP interface and SMBus interfaces are supported to connect a BMC with the Ethernet controller. The UMP uses either MII or RMII signaling. The SMBus interface block provides a serial interface that operates at clock speed of up to 400 kHz.

Figure 1: Functional Block Diagram

The BCM57710/BCM57711 device includes a Serial Flash Controller which implements the Serial Peripheral Interface (SPI) to connect to the serial flash devices which are used for storing the boot-code, device info, manufacturing info, and other firmware like PXE Option ROM image, UMP/NC-SI firmware, and IPMI firmware.

The MDIO interface block enables programming and control of the internal PHY (XGXS) and of the external PHY. The LED Control block implements the logic for controlling and driving various Ethernet link and PCIe link status signals. The GPIO block controls the four general purpose I/O pins and two special purpose I/O (SPIO) pins per port. Lastly, the JTAG block implements the IEEE 1149-1compliant JTAG support.

The Broadcom NetXtreme II includes dedicated hardware and processors that process the frames that traverse it and provide its functionality. On the transmit path, the Broadcom NetXtreme II copies the data directly from the highest hierarchy of buffers available (in prioritized order of application buffers, ULP buffers, TCP buffers) on the host; executes, when relevant, the L5 protocols; adds the iSCSI 1.0, or RDMA headers, followed by executing the TCP/IP and adding its headers, relieving the host CPU from these time-consuming operations. On the receive path, the Broadcom NetXtreme II processes the frame up to the highest layer of support present in the frame. Further, it removes the lower level headers from the frames it receives off the wire. It posts the data directly to application buffers, sparing host CPU resources that would otherwise be required for this activity.

For iSCSI, the Broadcom NetXtreme II provides hardware hooks for the most time-consuming tasks. On transmit, the Broadcom NetXtreme II copies data directly from the iSCSI buffers, and computes the header and data CRC when used. On receive, the Broadcom NetXtreme II strips off the framing headers and checks CRC prior to storing the data in the designated iSCSI buffers.

### TCP-OFFLOAD

The TCP/IP protocol suite is used to provide transport (L4) services for a wide range of applications. File transfer protocols like CIFS and NFS, to name a few, utilize the services of TCP/IP. For a long time, this protocol suite was run on the host CPU consuming a very high percentage of its resources and leaving little resources for the applications themselves. The BCM57710/BCM57711 includes a TCP Checksum Offload (CSO) feature and TCP Segmentation Offload (TSO) features, also known as Large Send Offload (LSO) that saves host CPU cycles.

The Broadcom NetXtreme II provides an industry-first TCP offload that is carefully architected for integration with the operating system, unlike many of the standalone TCP offloads. In basic terms, the Broadcom NetXtreme II architecture allows the operating system to provide control and management functions (such as connection setup, prevention of denial-of service attack, system resource allocation, selection of the most promising TCP/IP flows for offload, error and exception handling). The Broadcom NetXtreme II fully owns the data processing of TCP/IP flows offloaded to it. The Broadcom NetXtreme II is fully compliant with relevant Internet Engineering Task Force (IETF) RFCs and fully supports modern TCP options like time stamp, window scaling, and so on. The implementation also provides flexibility and robustness against potential changes to TCP algorithms like congestion control by implementing this functionality in firmware, making changes easy to manage.

On transmit, the DMA engine fetches data from the host memory, segments it to the size allowed by the network (MSS or maximum segment size), formats the TCP, IP, 802.2 (Logical Link Control), and Ethernet headers and sends it on the wire. The TCP/IP context that resides on-chip is updated accordingly (all the TCP/IP state variables and timers). If the frame has not reached its destination, the Broadcom NetXtreme II retransmits it according to TCP protocol rules. On receive, every frame is parsed, and if it is a valid frame (i.e., it passes all checks for Ethernet, IP, and TCP frame format and consistency) and it belongs to one of the connections offloaded to the Broadcom NetXtreme II, it is processed for TCP/IP. The processing includes the complete TCP/IP protocol state variables, header removal for Ethernet, IP and TCP. The data is either placed in a temporary anonymous buffer similar to a software stack today or is placed directly at the buffer pre-posted by the application (for example, Zero Copy), if the application had posted such buffer in advance. The Broadcom NetXtreme II fully handles out-of-order reception, including placement of data in the buffers (Zero Copy).

The Broadcom NetXtreme II TCP Offload functionality allows simultaneous operation of up to 1 million fully offloaded TCP connections. The Broadcom NetXtreme II TCP Offload significantly reduces the host CPU utilization while preserving the rich and flexible nature of the soft implementation of the operating system stack. As the TCP control loop is shorter (ACK messages and other control functions handled by hardware), TCP data exchange becomes faster and more efficient and latencies of TCP operation are reduced.

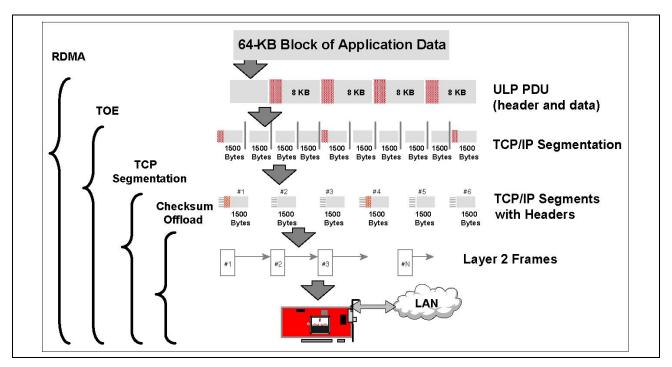

Figure 2 on page 8 shows an example of the basic flow of application data through the networking stack on its way to the wire. This data flow begins with the application writing a block of data (e.g., 64 KB) to the sockets interface. The application may insert application layer headers in the data (e.g., every 8192 bytes) and split it into 8 messages or PDUs. The networking stack further splits this into TCP segments, typically 1500 bytes each (also the typical MTU setting for Ethernet frames) to fit into standard Ethernet frames. The TCP stack then processes TCP and IP and adds the TCP/IP headers into each packet. The packet information is then posted to the NIC's output queue, and the NIC fetches the data from the host memory, calculates checksum and Ethernet CRC, and places it into the NIC buffers for transmission. The NIC transmits the information to the wire and interrupts the CPU to signal completion of the transaction.

Figure 2 on page 8 also illustrates the differences between the existing technologies of checksum offload and TCP segmentation, and between TCP Offload and RDMA. With checksum offload, the NIC calculates and appends the TCP/IP checksum to each outgoing packet, offloading the CPU of this task. TCP segmentation copies the packet header from one packet to the next in a string of like packets, further offloading the CPU of the creation of each packet header when sending large segments of data. TCP Offload even further offloads the CPU by allowing the NIC to handle the tasks associated with reliable transport (windowing, sequence numbers, packet acknowledgements, and so on) and by completely processing the received segments, placing the data in the buffers instead of the host stack. RDMA provides the ultimate offload by allowing

the RNIC to communicate directly with the application by bypassing the kernel, taking application data, creating segments, and handling TCP/IP and lower-layer functions to move the data directly into the receiver's application space. The RDMA's built-in header and data separation also eliminates the need to strip the application/middleware header.

Figure 2: Data Flow From Application Through Wire

#### **ISCSI OFFLOAD**

The IETF has standardized the Internet Small-Computer Systems Interface (iSCSI). The SCSI is a popular family of protocols that enable systems to communicate with storage devices, using block-level transfer (i.e., address data stored on a storage device that is not a whole file, unlike file-transfer protocols such as NFS or CIFS). iSCSI maps the SCSI request/ response application protocols and its standardized command set over TCP/IP networks. For further information on iSCSI, refer to RFC 3720.

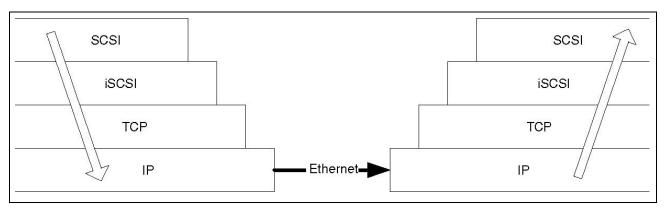

As iSCSI utilizes TCP as its sole transport protocol, it greatly benefits from hardware acceleration of the TCP processing (such as when using a TCP Offload). However, iSCSI as a layer 5 protocol has additional mechanisms beyond the TCP layer. Figure 3 on page 9 shows the relationship iSCSI has to TCP and to the SCSI layer. As is custom in the SCSI family, the initiator requests certain operations (e.g., IO read or IO write) from the target in an end-to-end SCSI session using iSCSI.

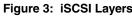

The iSCSI layer adds several mechanisms above and beyond the TCP transport service. The iSCSI frame shown in Figure 4 on page 9 is an iSCSI PDU embedded as the payload of a standard TCP/IP frame. To further enhance the TCP checksum mechanism, iSCSI optionally uses header and data digest (such as CRC-32c). As iSCSI exposes the use of a named buffer to both the initiator and the target, it also facilitates for direct data placement into these named buffers (for example, zero copy). These mechanisms benefit from hardware acceleration.

The Broadcom NetXtreme II targets best-system performance, maintains system flexibility to changes, and supports current and future OS convergence and integration. Therefore, the Broadcom NetXtreme II iSCSI offload architecture is unique as evident by the split between hardware and host processing. Unlike a monolithic implementation on an HBA, the Broadcom

#### BCM57710/BCM57711

## Programmer's Guide

09/25/09

NetXtreme II focuses mainly on offloading to hardware the time-consuming elements poorly handled by software. A monolithic implementation offloads the complete iSCSI protocol to the HBA. This adds complexity to the HBA in order to process the complete control plane, which is better handled by the host CPU, and limits the integration options with a host operating system (such as when the control plane on the host provides for flexible implementation and robustness against updates to the iSCSI protocol, allowing for virtually no limit on number of outstanding commands and no limit on number of connections per session, and so forth). The Broadcom NetXtreme II accelerates in hardware the iSCSI mechanisms that impact system resource utilization and performance. It supports all of these mechanisms with the support of specially built hardware circuitry and/or firmware executing on-chip. The Broadcom NetXtreme II provides rich and complete iSCSI HBA functionality.

#### Figure 4: iSCSI Ethernet Frame Encapsulation

The Broadcom NetXtreme II supports the iSCSI frame format, header/data separation, insertion and checking of the iSCSI header and data CRCs, and direct data placement into the named iSCSI buffers. A deep command queue ensures optimal utilization of the network for maximal bandwidth and a high number of I/O Operations Per Second (IOPS) under significantly reduced CPU utilization.

Figure 5 on page 10 depicts a typical data flow between an iSCSI initiator and an iSCSI target. The Broadcom NetXtreme II can be the core of an initiator HBA. The initiator's SCSI driver passes SCSI Control Data Blocks (CDBs) to the iSCSI layer that sits atop the TCP/IP stack. On the target, a storage device (for example, a SCSI disk) sees SCSI commands and has no knowledge of the iSCSI layer. The SCSI disk interprets the SCSI commands, executes them, and sends appropriate data or replies to its local iSCSI layer, which transports them to the iSCSI on the initiator.

Figure 5: iSCSI Architecture

## **REMOTE PHY**

The goal of traditional pass-through copper switch modules in a Blade Server environment is to provide the same or similar functionality as a local copper PHY. Presently, pass-through modules only support a Gigabit Interface Connection (GBIC) mode of operation. There are several limitations to this approach; The GBIC only supports functionality enabled by the autonegotiation base page exchange of Clause 37 of the IEEE 802.3; limited to duplex, and pause resolution. The speed of 1 Gbps is assumed. Extended features such as 10 Mbps and 100 Mbps, jumbo frame support, Ethernet at wire-speed, and so forth, are not supported and not possible.

Remote PHY addresses the need to provide a similar feature set as a local copper PHY. The remote PHY protocol is PHY vendor independent since all communication is handled via the extension of clause 37 of the IEEE 802.3 specification. Industry standard mechanisms are used to establish the link. The Remote PHY protocol uses the appropriate 1000BASE-KX signaling as defined in the IEEE 802.3ap specification for backplane operation.

The Broadcom Remote PHY SerDes Autonegotiation Mode (BAM) utilizes the IEEE 802.3 next page capabilities in Clause 37 to support the Remote PHY feature. The remote copper PHY features are abstracted by mapping these features onto the exchange of the next pages during the autonegotiation process. Explicit registers and the mapping of features are not required by the link partner. This lowers the cost of ownership as new features can be easily supported by additional capabilities and pages on the standardized autonegotiation exchange of pages. The Remote PHY feature set is supported in hardware in the Broadcom NetXtreme II with the possibility of expanding the feature set under firmware control.

The Broadcom NetXtreme II supports the Remote PHY feature where the SerDes interfaces to a remote 10/100/1000BASE-T copper PHY via a backplane. Since all the PHY management communication is performed in-band using the SerDes interface during autonegotiation, no out-of-band Management Data I/O (MDIO) bus is required. Remote PHY supports all standard functions of a 10/100/1000BASE-T copper PHY such as autonegotiation, forced speeds, Ethernet at wirespeed, and auto MDIX functions.

A remote copper PHY is a stand-alone copper PHY transceiver that connects to the local MAC via a backplane and communicates to another copper transceiver via category 5 (CAT5) copper cabling. The copper interface is governed by Clauses 14, 24, 28, and 40 of IEEE 802.3 for 10T, 100T, autonegotiation, and 1000T, respectively. The SerDes interface is governed by Clauses 36 and 37 of IEEE 802.3 for 1000-X as well as the Broadcom proprietary SerDes BAM.

## BASIC OPERATION BETWEEN DEVICE AND REMOTE COPPER PHY

The remote copper PHY operates with two asynchronous autonegotiation processes running. One operates on the copper media and is based on clause 28 of the IEEE 802.3 standard. The other operates on the SerDes media or backplane and is based on Clause 37 of the IEEE 802.3 standard as well as the Broadcom proprietary SerDes BAM. There are some connections between the two autonegotiation processes that allow one to restart the other.

The copper interface will restart the SerDes interface under the following conditions:

- The copper interface receives advertised abilities from its link partner that are different than the advertised abilities transmitted on the SerDes interface. This includes 10,100, 1000T half duplex and full duplex, and pause settings.

- The copper link change (goes up or goes down)

- The copper autonegotiation changes from enabled to disabled and the current SerDes transmitted advertised abilities are different from the register 0x04 SerDes advertisement register.

The SerDes interface will restart the copper interface under the following conditions:

• The SerDes interface receives advertised abilities from its link partner that are different than the advertised abilities transmitted on the copper interface. This includes 10, 100 and 1000T half duplex and full duplex and pause settings.

• The SerDes autonegotiation changes from enabled to disabled and the current copper transmitted advertised abilities are different from the register 0x09 copper advertisement register.

The SerDes interface will exchange autonegotiation base pages between the MAC/switch and the RemotePHY. Following the base page, the next pages are exchanged.

The remote copper PHY updates all of its control settings from the MAC/Switch on entry to HCD/link (highest common denominator) determination. The settings are stored internally by the remote copper PHY until one of the following occurs:

- Another sequence of next pages is exchanged after restarting the SerDes autonegotiation for any reason. If the new

next page exchange does not contain a MAC/Switch with remote copper capability, then the remote copper PHY

register settings revert back to the default settings. If it is a MAC/Switch with remote copper capability, then any changes

will be updated by the remote copper PHY.

- The local SerDes autonegotiation is disabled for any reason and detects valid idles from the serdes link partner (i.e. parallel-detection). The remote copper PHY register settings will revert back to the default settings.

- The RemotePHY SerDes link partner sends SGMII autonegotiation code words and the RemotePHY automatically changes to SGMII mode (if SGMII/GBIC auto-detection is enabled) and a base page is received without a selector mismatch. The remote copper PHY register settings will revert back to the default settings.

The simplified hardware architecture is shown in Figure 6.

Figure 6: Simplified Hardware Architecture

09/25/09

## SerDes

The BCM57710/BCM57711 integrates dual XAUI™/10GBASE-CX4/10GBASE-KX4 transceivers to support the 1-/2.5-/10-Gbps speeds of operation on both the ports. Each of the ports can be individually selected for XAUI or 10GBASE-CX4 or 10GBASE-KX4 or 1000BASE-KX or 2500BASE-KX mode of operation. The XAUI (10-gigabit attachment unit interface) is referenced in the IEEE 802.3ae specification and it consists of four lanes each running at 2.5 Gbps (3.125 Gbaud) for an aggregate bandwidth of 10 Gbps. A single lane of the XAUI can be configured to operate at either 1-Gbit or 2.5-Gbit data rates.

There are two Ethernet ports coincident with the two XAUI ports.

Figure 7 on page 14 illustrates the top level multiplexing of the two XAUI interfaces (Unicore x4 1000/2500). The two 1000/2500 BASE-KX SerDes interfaces shown are not used in the BCM57710 and are not connected in the BCM57711. The two Unicore x4 blocks are connected to two instances of the 10-Gbps MAC (also known as Big MAC) via two 2:1 multiplexers. The 2:1 multiplexers allow connecting any of the two Unicore blocks to any of the two Big MACs. When configured for 1/2.5 Gbps operation, the lane swap logic controls the two Unicore blocks so that a single lane can be controlled by the EMAC.

Figure 7: Multiplexing b/w XAUI and 1000BASE-KX/2500BASE-KX

### MAC

As shown in Figure 7 on page 14, the BCM57710/BCM57711 implements one EMAC and one Big MAC for each of its two ports. The EMAC is used for 1-Gbps/2.5-Gbps operation and Big MAC is used for 10-Gbps operation. Both the EMAC and Big-MAC perform all of the following Ethernet MAC functionalities.

On the receive side:

- Adapts data presented at the frequency of the network clock to that of the system clock.

- Interprets /Idle/, /Start/, /Term/, and /Error/ special control characters.

- Recognizes the start and end of Ethernet packets.

- Recognizes packet framing errors.

- Strips the preamble from packets.

- Checks the FCS field for compliance to the IEEE CRC function.

- Optionally strips the FCS field from incoming packets.

- Eliminates all incoming packets less than 64 bytes in length.

- Truncates incoming packets of greater than a programmable size limit.

- Detects SAFC control frames and transfers them to the transmit processor.

- Eliminates all incoming MAC Control packets, or transfers them to the transmit processor for congestion management support.

- · Asserts an error signal for all packets passed to the system on which errors are detected.

- Recognizes Pause packets and signals the transmit section to hold off data transfers as necessary.

- Detects Link Fault Sequences

On the transmit side:

- Synchronizes data from the system to the network clock.

- Encapsulates the data in a valid Ethernet packet

- Flags outgoing packets of less than 64 bytes in length with an error.

- Truncates outgoing packets of size greater than a programmable limit and flags them with errors.

- As a programmable option per packet, either appends a valid FCS to all packets presented by the system, or keeps the FCS unchanged, or replaces the FCS with a newly computed value.

- Generates and sends Pause packets as per IEEE 802.3 clause 31 either at the request of the system or upon receiving a signal from the receive section of MAC.

- Maintains packet statistics

- Transmits Link Fault Sequences

The EMAC also provides the PHY management interface via the MDC/MDIO pins for all 1-/2.5-/10-Gbps speeds. Each of the EMACs has an MDIO controller. The EMAC has to be out of reset for MDIO to work.

### **RECEIVE FRONT END**

The Arbiter/Filter, Receive Buffer, Parser and Connection lookup blocks shown in the Figure 6: "Simplified Hardware Architecture," on page 12 constitute the Receive Front End (RFE) of the device. The RFE module receives the traffic from the two ports and the internal loopback port, buffers the data, parses the packet headers, and searches for the connection in the connection database. All the sub-blocks of RFE module are described below.

#### NETWORK INTERFACE GLUE

The Network Interface Glue (NIG) receives packets from two 10G MAC cores, and loop-back packets from the transmitter. This block synchronizes the packets from the MAC cores to the system clock, performs the bus adaptations, and forwards the packets to BRB. It is also responsible for counting packet length, discarding packets in case of backpressure, maintaining per port EOP (end of packet) information, and collecting statistics.

#### ARBITER/FILTER

The arbiter/filter selects the port that gains the access to the BRB, decides whether an incoming packet should be written to the BRB, the Mgmt Rx Buffer or both, or (in the case of congestion management frames) to the transmit processor and selects between the Mgmt Tx packet, Host packet, and debug packet for transmission on the wire. It uses the Round Robin algorithm to provide fairness between all write clients to the BRB.

#### **BIG RECEIVE BUFFER**

The Big Receive Buffer (BRB) is used to buffer packets (up to jumbo packet size) from each of the interfaces until they are parsed and validated by the Parser and the TCP processing engine. The BRB is also used to absorb temporary traffic bursts, where the input packet rate is higher than the device packet processing rate. The BRB is 128 KB in size and supports a 32-Gbps input bandwidth and 32-Gbps output bandwidth. It is logically divided in to 256-byte blocks that are managed by link-lists to optimize utilization.

Every incoming packet is written to the BRB as long as it has space for a new packet coming on a given port. Per port buffer space guaranteed can be configured, while the remaining buffer space is shared between the two network ports and traffic coming on the loopback interface from the transmitter. In parallel, the BRB sends a message to the Parser informing about the new packet and its address in the buffer. The BRB also initiates the Pause frame transmission when it is almost full and Pause is enabled.

## PARSER

For every incoming packet, after the header is received, the BRB sends a message to the Parser with the corresponding port number, the start block, Flush indication flag and the port tag. This message is queued until it can be handled by the Parser. The queue is global for all the ports. The parser is responsible for parsing the Ethernet, IPv4, IPv6, TCP and UDP headers, calculating the TCP/UDP checksum, calculating the MPA CRC assuming single aligned PDU and for building the messages to the L4 Rx Processor (aka TCP-Receiver). The header parsing includes:

- Ethernet address type recognition

- Validation of version and length fields

- Fragments recognition

- Validation of IP header checksum

- TCP options parsing for time-stamp

After the header parsing, messages are sent to the Context Fetch Controller (CFC). This unit is also commonly referred to as a Memory Management Unit (MMU) for connection information, and to the searcher to calculate Hash on the TCP/IP 4-tuple (for RSS). If the CFC cannot find the connection information in its internal cache, it requests the searcher to do a search for the connection information in host memory and to load the connection context to its internal cache. Note that the parser sends the Search message to the CFC only when the parsing is successful and the received packet is a TCP packet. After the responses are returned from the CFC and the searcher, the Parser builds a message to the TCP-Receiver RISC (aka TCP-Receiver STORM or L4 Rx Processor). The message mainly includes general parameters, header parsing information, TCP parameters, some context parameters from the CFC, and the RSS Hash result from the searcher.

For every non-fragmented TCP packet, the TCP checksum is calculated. In addition, for each TCP packet, the MPA CRC is also calculated simultaneously. The MPA CRC calculation is speculative and it assumes single aligned PDU in the TCP packet. When checksum and MPA CRC calculations are completed, and the EOP information is received from the NIG, the Parser generates a second message to the TCP-Receiver STORM, with the packet length, EOP info and the calculation results. The split of information to TCP-Receiver STORM into two messages is done in order to save latency by starting the TCP processing after the header is received but before the packet is fully received.